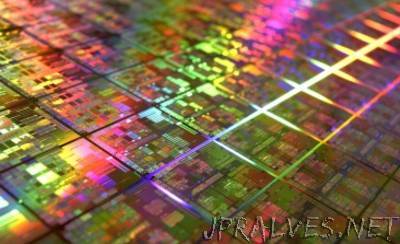

“Trying to cover the waterfront, TSMC disclosed plans for new high-, mid- and low-end processes at an annual event here. They included an enhanced 7nm FinFET node using extreme ultraviolet lithography, a 12nm upgrade of its 16nm process and a 22nm planar technology — its answer to fully depleted silicon-on-insulator (FD-SOI). The foundry also described enhancements to its two chip-stacking techniques, advances in RF CMOS and work in transistors and materials, paving the way to a 3nm node and beyond. In addition, it previewed design capabilities using machine learning that it will offer before the end of the year.”