Other

“The MK1 CPU is composed of several modules, all connected trough a common 8-bit BUS, the status of each module is shown by dedicated LEDs. The clock module is designed to allow step-by-step execution; in automatic mode the clock speed …

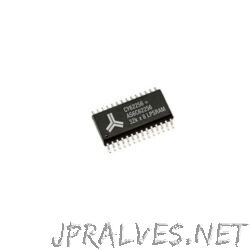

The CY62256 is a high-performance CMOS static RAM organized as 32K words by 8 bits. Easy memory expansion is provided by an active LOW chip enable (CE) and active LOW output enable (OE) and three-state drivers. This device has an automatic power-down feature, reducing the power consumption by 99.9% when deselected. An active LOW write enable signal (WE) controls the writing/reading operation of the memory. When CE and WE inputs are both LOW, data on the eight data input/output pins (I/O0 through I/O7) is written into the memory location addressed by the address present on the address pins (A0 through A14). Reading the device is accomplished by selecting the device and enabling the outputs, CE and OE active LOW, while WE remains inactive or HIGH. Under these conditions, the contents of the location addressed by the information on address pins are present on the eight data input/output pins. The input/output pins remain in a high-impedance state unless the chip is selected, outputs are enabled, and write enable (WE) is HIGH.

“The MK1 CPU is composed of several modules, all connected trough a common 8-bit BUS, the status of each module is shown by dedicated LEDs. The clock module is designed to allow step-by-step execution; in automatic mode the clock speed …