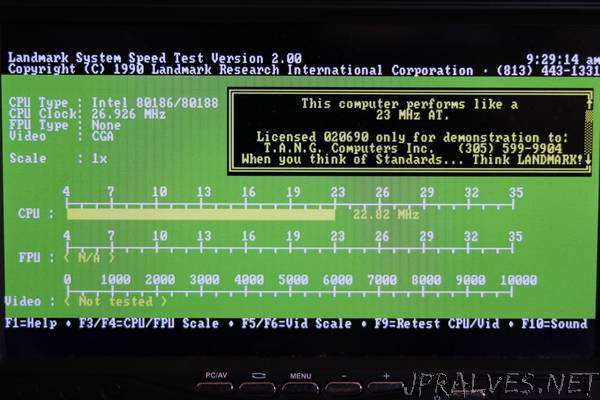

“The S80186 IP core is a compact, 80186 binary compatible core, implementing the full 80186 ISA suitable for integration into FPGA/ASIC designs. The core executes most instructions in far fewer cycles than the original Intel 8086, and in many cases, fewer cycles than the 80286. The core is supplied as synthesizable SystemVerilog, along with a C++ reference model, extensive tests, a reference BIOS implementation and reference FPGA designs. The core is released under the GPLv3 license.

Architecture

The S80186 is a 16-bit architecture with 8 16-bit general purpose registers, 4 segment registers allowing access to 1MB of physical memory. The architecture uses a variable length instruction encoding allowing for high code density. The core is a microcoded design using a small amount of logic and a flexible microassembler. The microsequencer is used to implement an efficient debug interface that can be connected to a JTAG TAP or disabled if required.

Full compatibility with 80186 ISA is provided, implementing all instructions, traps, faults and interrupts and known errata. Undocumented instructions such as SETALC are also implemented.

Software

The S80186 core is compatible with the Intel 80186 and so enjoys extensive software compatibility. There are a wide range of development tools available including OpenWatcom, GCC and NASM, and the core can run existing operating systems such as MS-DOS and FreeDOS. A sample BIOS implementation is provided for the FPGA designs.”