“A Forth CPU and System on a Chip, based on the J1, written in VHDL

This project implements a small stack computer tailored to executing Forth based on the J1 CPU. The processor has been rewritten in VHDL from Verilog, and extended slightly.

The goals of the project are as follows:

Create a working version of J1 processor (called the H2).

Make a working toolchain for the processor.

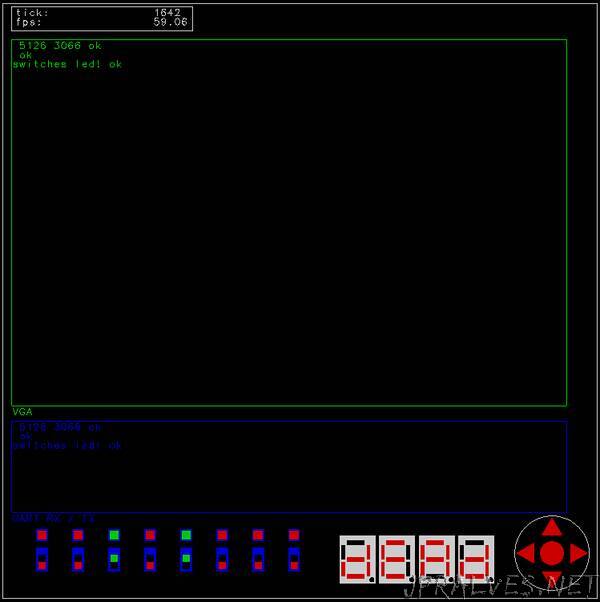

Create a FORTH for the processor which can take its input either from a UART or a USB keyboard and a VGA adapter.

All three of which have been completed.

The H2 processor, like the J1, is a stack based processor that executes an instruction set especially suited for FORTH.

The current target is the Nexys3 board, with a Xilinx Spartan-6 XC6LX16-CS324 FPGA, new boards will be targeted in the future as this board is reaching it’s end of life. The VHDL is written in a generic way, with hardware components being inferred instead of explicitly instantiated, this should make the code fairly portable, although the interfaces to the Nexys3 board components are specific to the peripherals on that board.”