“A re-creation of a Cosmic ELF computer, Coded in SpinalHDL

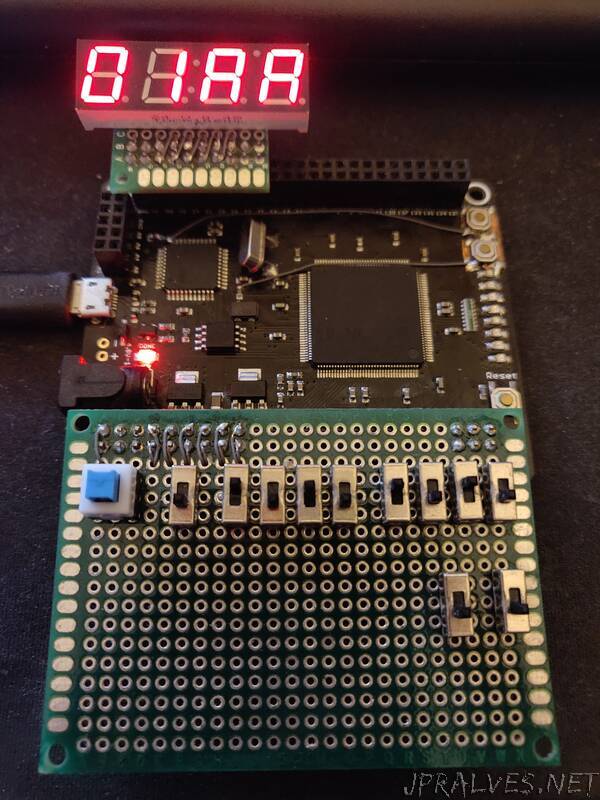

This is a re-creation of a Cosmac ELF computer, Coded in SpinalHDL.

The goal of this project is to end up with a cycle-accurate 1802 processor that can be used in FPGA designs easily. When I start the project I was new to SpinalHDL but I had attempted in the past to write the same processor in VHDL. However, language complexity and the sheer amount of code and time needed to write and debug that project ended the work on it.

To make verification of the CPU easier, I made the simulation capable of reading the Emma debug trace log format. The theory is that the CPU should follow that same path as the debug log from Emma.

If the Address or D register doesn’t match the one in the log, then there is an issue and it will halt the simulation at that point. Using GTKWave you can view the output of the simulation and debug the issue.

The test program included uses the Floating Point Subroutines by Paul Wasserman. I copied the subroutine listings by hand into a hex editor and checked them by overlaying an image of the hex code I copied, with the scanned images. Included is a copy of the scans, and a copy of the binary file for the subroutines. Along with the assemble code I wrote to test the CPU.

If you would like to learn more about the 1802 processor here’s a video about the designer Joseph Weisbecker, For information about the Cosmac Elf computer there’s the wiki page.”