Other

“Control anything with your remote control. This receiver works with RC-5 and NEC format IR remote controls, depending on the firmware used. The receiver has 11 output channels, and each channel can have up to 4 buttons (on, off …

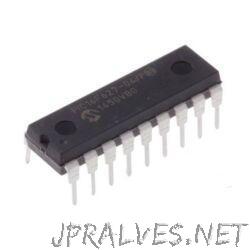

The high performance of the PIC16F62X family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16F62X uses a Harvard architecture, in which, program and data are accessed from separate memories using separate buses. This improves bandwidth over traditional Von Neumann architecture where program and data are fetched from the same memory. Separating program and data memory further allows instructions to be sized differently than 8-bit wide data word. Instruction opcodes are 14-bits wide making it possible to have all single-word instructions.

“Control anything with your remote control. This receiver works with RC-5 and NEC format IR remote controls, depending on the firmware used. The receiver has 11 output channels, and each channel can have up to 4 buttons (on, off …