Other

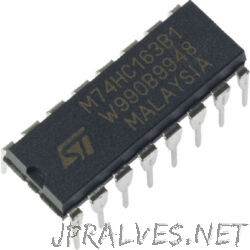

“After various experiments and failed attempts to design a 7400-based computer, I came to a quite minimalistic 8-bit approach which is nevertheless pretty versatile and can utilize a surprisingly large amount of memory resources. The CPU core itself executes its …

“I came across this weird chip a few months ago. Designed by Motorola in the 70s, its purpose is to replace the “ladder logic” relays in industrial process control so all it needs to do is make simple decisions based …