Other

“Several years ago, a scammer woke me up at 4 am. Some nonsense about me “owing to the IRS”. A few months later, some clueless telemarketer forgot about the existence of time zones and rang me up at 6 am …

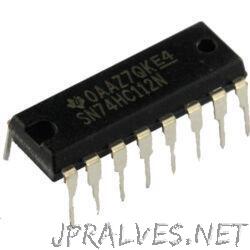

The 74HC112; 74HCT112 is a dual negative-edge triggered JK flip-flop. It features individual J and K inputs, clock (nCP) set (nSD) and reset (nRD) inputs. It also has complementary nQ and nQ outputs. The set and reset are asynchronous active LOW inputs and operate independently of the clock input. The J and K inputs control the state changes of the flip-flops as described in the mode select function table. The J and K inputs must be stable one set-up time prior to the HIGH-to-LOW clock transition for predictable operation. Inputs include clamp diodes that enable the use of current limiting resistors to interface inputs to voltages in excess of VCC. Schmitt-trigger action in the clock input makes the circuit highly tolerant to slower clock rise and fall times.

“Several years ago, a scammer woke me up at 4 am. Some nonsense about me “owing to the IRS”. A few months later, some clueless telemarketer forgot about the existence of time zones and rang me up at 6 am …