“IBM Research and Tokyo Electron have partnered on a chipmaking innovation that simplifies the supply chain and process for producing wafers with 3D chip stacking technology.

The demand for computer chips has never been higher, but the last two years have put unprecedented pressure on global supply chains. But even before then, there were pressures on the computer chip industry. Moore’s Law, which postulated that the number of transistors on a microchip would double each year, started to strain as chipmakers approached the physical limits of silicon. IBM Research’s smallest chip node to date is only 2 nanometers wide, for example.

Our latest breakthrough explores how chips could be stacked to simplify the supply chain for producing chips. Today, we’re announcing with our partner Tokyo Electron (TEL), that we’ve successfully implemented a new process for producing 300 mm silicon chip wafers for 3D chip stacking technology, the world’s first at the 300 mm level. Chip stacking, which is currently only employed in high-end operations like the production of high-bandwidth memory, has the potential to expand the number of transistors in a given volume — rather than an area, as Moore’s Law has traditionally been interpreted as focusing on.

Turning up the (3D) volume

Chip stacking architecture requires vertical connections between layers of silicon, called through-silicon vias (TSVs) — miniscule connections that allow for a current to flow between one silicon layer to another, allowing each layer to talk to the others. The process entails thinning the backside of the silicon wafer to reveal and complete the fabrication of TSVs required for vertical stacking. The layers that make up a chip stack are extremely thin, typically less than 100 microns thick.

To ensure these fragile and flexible silicon wafers make it through the production process, each wafer is attached to what’s called a carrier wafer. In modern chipmaking, these carrier wafers are usually made of glass, which is temporarily bonded to the silicon to ensure that it can be processed without being damaged. Once the wafer has been processed, the glass carrier is removed from the silicon using ultraviolet lasers to release the bond between the two layers. In some cases, a silicon carrier wafer can be used, but this requires the release process to employ a mechanical force to facilitate separation, which can introduce defects and yield loss.

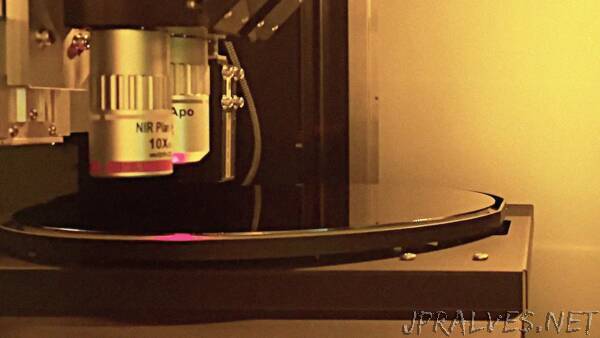

IBM and TEL have collaborated to create a new 300 mm module using an infrared laser to enable a debonding process that’s transparent to silicon, meaning that standard silicon wafers can be used instead of glass wafers for the carrier.

With our new technology, silicon wafers can be bonded to other pieces of silicon, meaning glass no longer has to be introduced into the production line. There are also fabrication advantages associated with processing bonded silicon wafer pairs, such as eliminating tool compatibility and chucking issues, fewer defects, and process issues associated with dissimilar wafer pairs, as well as enabling inline testing of thinned wafers. This technology enables advanced FOWL and 3D chiplet technologies using silicon interconnects that scale very well.

IBM Research has been working with TEL since 2018 to perfect this new type of laser debonding, and it’s just the latest collaboration in a partnership that dates back more than 20 years. Since 2018, TEL, who are experts in designing the tools needed to produce new silicon chips at scale, has taken this process technology, and designed and built a new 300mm module capable of releasing and separating bonded silicon wafer pairs for volume manufacturing.

Together, we built a beta tooling system in Albany, New York, where there is a rich ecosystem around the production, design, and fabrication of semiconductors — in which we play an active role. Next, we’ll further test our beta system to demonstrate how this process will be implemented into a full semiconductor manufacturing flow to demonstrate a full 3D chip stack built using our process.

As the global chip shortage continues, we’ll likely need novel ways to increase chip production capacity over the coming years. We hope our work will help cut down on the number of products needed in the semiconductor supply chain, while also helping drive processing power improvements for years to come.”