Other

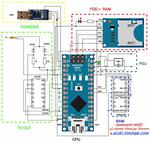

“I will begin here with a description of my project cpm4nano - a CP/M-compatible computer based on the Arduino Nano 3.0. Currently one (!) Arduino Nano (!) in my project: emulates the i8080 processor, 64 KBytes RAM+additional banks, 4 FDD …

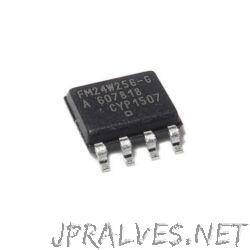

The FM24C256/C256L/C256LZ devices are 256 Kbits CMOS nonvolatile electrically erasable memory. These devices offer the designer different low voltage and low power options. They conform to all requirements in the Extended IIC 2-wire protocol. Furthermore, they are designed to minimize device pin count and simplify PC board layout requirements. The entire memory array can be write disabled (Write Protection) by connecting the WP pin to VCC. Functional address lines allow up to eight devices on the same bus, for up to a total of 2 Mbit address space. The IIC communication protocol uses CLOCK (SCL) and DATA I/O (SDA) lines to synchronously clock data between the master (for example a microprocessor) and the slave EEPROM device(s).

“I will begin here with a description of my project cpm4nano - a CP/M-compatible computer based on the Arduino Nano 3.0. Currently one (!) Arduino Nano (!) in my project: emulates the i8080 processor, 64 KBytes RAM+additional banks, 4 FDD …