Other

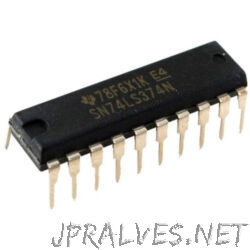

“A minimal 6502 computer that can be programed machine language without PCs I have developed a minimal 6502 computer that can be programed machine language without PCs. The concept is the following three. (1) Minimize the number of peripheral standard …