“Using the Genesys ZU 3EG to implement an image processing pipeline with the latest Xilinx image processing IP cores.

Image processing is at the heart of many applications from simple embedded vision to autonomous vehicles and drones. The Xilinx MPSoC with its built in DisplayPort capability and support for MIPI DPhy in the programmable logic IO makes a great embedded vision platform.

These capabilities enable us to create a complex embedded vision and vision based processing systems which use artificial intelligence and machine learning.

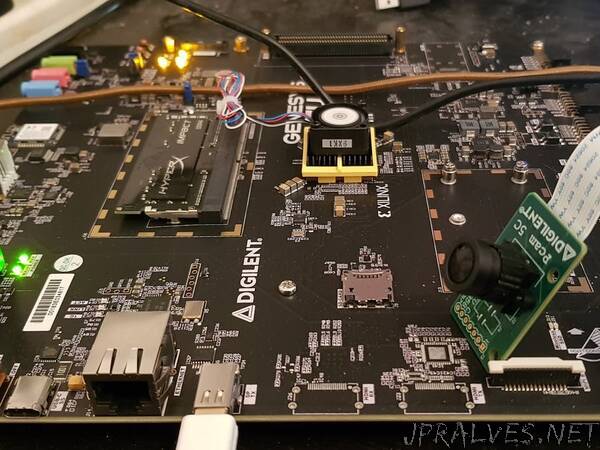

In this project we are going to explore getting an image processing chain up and running using the PCAM and Display Port. We can then add in High Level Synthesis IP cores to further process the image to demonstrate the capabilities of the board.

Programmable Logic Design

To get started with this design we need to have the Genesys ZU EG board support files installed within Vivado. If we do not have them we can download them from here. Install these file to the following location in your Vivado installation as shown below, note I placed the entire folder in.

With this completed we are ready to start with the development of the hardware design.

Within our design we are going to include the following IP

Zynq MPSoC Processing System - Processing system configured to enable the DisplayPort, I2C and GPIO EMIO

MIPI CSI2 RX Sub System - Receives the MIPI CSI2 stream from the PCAM.

Sensor Demosaic - Convert the RAW pixel format into a RGB pixel format.

Gamma LUT - Corrects image for gamma

VDMA - Writes the image to DDR memory in the processor system

Video Timing Generator - Generates the Output video timing

AXIS to Video Out - Converts from AXI Stream to parallel video

Clock Wizards - used to generate the video pixel clock and MIPI CSI2 reference clock

Along with the IP we also need to consider the clocking architecture, for this solution we implement the following approach

AXI Clock - 150 MHz - This clocks the AXI Stream and the AXI lite interface

DPHY Reference - 200 MHz - generated by clock wizard

Pixel Clock - 74.25 Mhz - used for 1280 by 720 at 60 FPS - generated by clock wizard

The completed block diagram should look like below, with the cores configured as shown.”