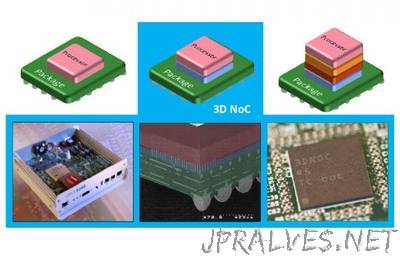

“Leti, a CEA Tech institute, today announced it has developed a new on-chip communications system to improve high-performance computing (HPC) that is faster and more energy efficient than current solutions and is compatible with 3D architectures. Leti researchers, working in the frame of IRT Nanoelec, boosted computing power and slashed energy consumption by stacking chips on top of each other in a single enclosure, or by placing the chips side by side on a silicon interposer. The chips, which have progressed from demonstrator to fabrication-ready, exchange data via a new communications network that is part of the network on chip (NoC) called 3D-NoC.”