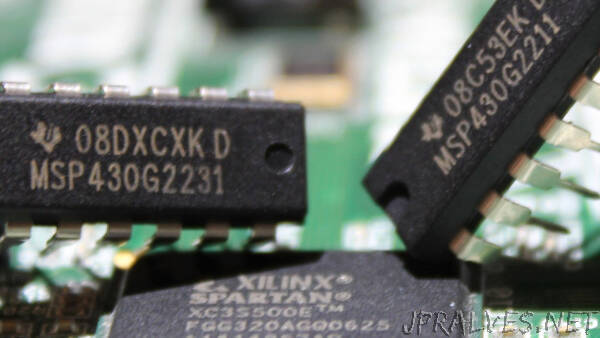

“A tiny (really tiny!) msp430-native microcontroller-like processor system written in platform independent VHDL

There is a pretty gap in the landscape of open-source soft-core processors between the tiny 8-bit processors and the chunky 32-bit ones. So I decided to fill this gap with a msp430-native 16-bit processor.

Introduction

The NEO430 is a TI msp430-native tiny microcontroller-like processor system. The system is highly configurable and provides of standard IO and peripheral components. If a certain module is not required at all it can be disabled and thus will not be synthesized. The project features Makefiles for Linux / Powershell / Windows’ Linux Subsystem and provides driver libraries for all peripheral devices as well as example programs.

To get the complete information overload take a look at the NEO430 Datasheet.

Differences to the Original MSP430 Processor

The NEO430 provides full ISA-compatibility to the original msp430 CPU. However, there are some differences. Here are the most important ones:

- Completely different processor modules with different functionality

- Up to 48kB instruction memory and 12kB data memory

- NEO430 tool chain (makefiles, boot-code and linker script) required for application compilation

- No support of CPU’s DADD operation

- Different numbers of instruction execution cycles

Processor Feature

- 16-bit open source soft-core microcontroller-like processor system

- Full support of the original MSP430 instruction set architecture (except for the DADD instruction)

- Code-efficient CISC-like instruction capabilities

- Tool chain based on free TI msp430-gcc compiler

- Application compilation scripts (makefiles) for Windows Powershell / Windows Subsystem for Linux / native Linux

- Completely described in behavioral, platform-independent VHDL (no macros, primitives, attributes, etc. used)

- Fully synchronous design, no latches, no gated clocks

- Very low resource requirements and high operating frequency

- Internal DMEM (RAM, for data) and IMEM (RAM or ROM, for code), configurable sizes

- Customizable processor hardware configuration:

- Optional multiplier/divider unit (MULDIV)

- Optional high-precision timer (TIMER)

- Optional universal asynchronous receiver and transmitter (UART)

- Optional serial peripheral interface (SPI), 8 or 16 bit tansfer data size, 6 dedicated CS lines

- Optional I2C-compatible two wire serial interface (TWI) supporting clock stretching

- Optional general purpose parallel IO port (GPIO), 16 inputs & 16 outputs, with pin-change interrupt and PWM option

- Optional 32-bit Wishbone bus interface adapter (WB32) - including bridges to Avalon (TM) bus and AXI4-Lite (TM)

- Optional watchdog timer (WDT)

- Optional cyclic redundancy check unit (CRC16/32)

- Optional custom functions unit (CFU) for user-defined processor extensions

- Optional 4 channel PWM controller with 4 or 8 bit resolution (PWM)

- Optional Galois Ring Oscillator (GARO) based true random number generator (TRNG) with de-biasing and internal post-processing

- Optional external interrupts controller with 8 independent channels (EXIRQ), can also be used for software-triggered interrupts (traps, breakpoints, etc.)

- Optional NCO-based programmable frequency generator with 3 independent channels (FREQ_GEN)

- Optional internal bootloader (2kB ROM) with serial user console and automatic boot from external SPI flash (like the FPGA configuration storage)”